### User Manual HVS/UM9802

#### **REVISION HISTORY**

| Version | Remarks                                                                                                                                                                                                                                                                                                                                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1     | DRAFT; 14.08.96                                                                                                                                                                                                                                                                                                                                                |

| 0.2     | Update I <sup>2</sup> C REGs 24,25; 20.08.96                                                                                                                                                                                                                                                                                                                   |

| 0.3     | Update REG7: ENA_HWE_ROUGH; 21.08.96                                                                                                                                                                                                                                                                                                                           |

| 1.0     | First Release; refers to BESIC-SW from V0.34 until V1.0; 31.10.96                                                                                                                                                                                                                                                                                              |

|         | (This UM describes the I <sup>2</sup> C interface of the BESIC for a single memory concept or a PROZONIC concept. The $\mu$ C ROM of the first BESIC samples contain this interface.                                                                                                                                                                           |

|         | MELZONIC control (SAA4991) is not possible via the I <sup>2</sup> C interface described in this document)                                                                                                                                                                                                                                                      |

| 2.0     | Second Release; refers to BESIC-SW starting with V2.0; 28.02.97                                                                                                                                                                                                                                                                                                |

|         | This document describes a new I <sup>2</sup> C interface of the BESIC including the MEL-<br>ZONIC control in addition to the features described in the first release document. An<br>external µC ROM of the first BESIC samples will contain this new I <sup>2</sup> C interface. A<br>new BESIC version, which will be developed, contains the new interface. |

| 2.1     | HVS/UM9704, 12.12.97, update of UM9701 V2.0                                                                                                                                                                                                                                                                                                                    |

| 1.0     | HVS/UM9802, 06.02.98<br>This user manual refers to the final BESIC version SAA 4977 V1C. This software sup-                                                                                                                                                                                                                                                    |

Purchase of Philips  $I^2C$  components conveys a license under the Philips  $I^2C$  patent to use the components in the  $I^2C$  system, provided the system conforms to the  $I^2C$  specifications defined by Philips.

#### © Philips Electronics N.V. 1998

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

User Manual HVS/UM9802

## USER MANUAL

## HVS/UM9802 I<sup>2</sup>C-bus Register Specification for the SAA 4977 V1C

Report No.: HVS/UM9802

Keywords

BESIC Memory Controller I<sup>2</sup>C-Bus PROZONIC MELZONIC

Date: <6st February, 1994>

3

## User Manual HVS/UM9802

#### Preface

The user manual describes the  $I^2C$ -bus register interface of an IPQ slave microcontroller (80C51 core), which is a part of the BESIC (SAA 4977). The described interface refers to the BESIC version V1C (see Revision History).

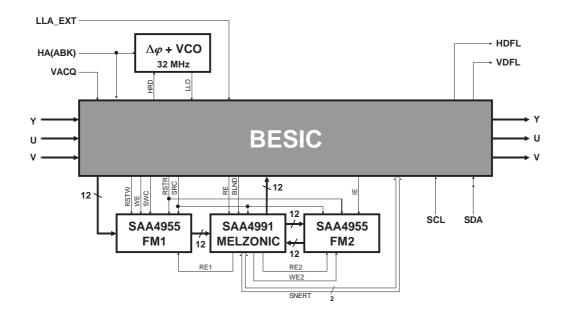

The BESIC is a videoprocessing IC providing analog interfacing, video enhancing features, memory controlling and the embedded 80C51 microprocessor core. The internal (slave) microcontroller is used as an interpreter between a main (master)  $\mu$ C and the Datapath Control in BESIC. It controls the embedded memory controller as well. In case of a two field memory concept either the PROZONIC (SAA4990; external) or MELZONIC (SAA4991; external) is supported by the software. In the single field concept the LIMERIC (SAA 4945) can be controlled via the SAA 4977 as well.

The software of the SAA 4977 V1C is written according to the Software Creation Process [9].

### User Manual HVS/UM9802

#### CONTENTS

| 1. | 1.1                 | Definition                | s, Acronyms and Abbreviations                                 | , |

|----|---------------------|---------------------------|---------------------------------------------------------------|---|

|    | 1.2                 | Reference                 | es                                                            |   |

| 2. | 2.1                 | Descriptio                | n of the different hardware concepts.                         | 3 |

|    | 2.2                 |                           | grams                                                         |   |

|    |                     | 2.2.1                     | SAA 4977 block diagram                                        |   |

|    |                     | 2.2.2                     | Single field concept                                          |   |

|    |                     | 2.2.3                     | PROZONIC concept                                              |   |

|    |                     | 2.2.4                     | MELZONIC concept                                              | ) |

| 3. | 1 <sup>2</sup> C-bu | s interface               | <b>.</b>                                                      |   |

|    | 3.1                 |                           | of the interface                                              |   |

|    | 3.2                 |                           | lata to the IPQ $\mu$ C                                       |   |

|    | 0.2                 | 3.2.1                     | $I^2C$ transmission protocol                                  |   |

|    |                     | 3.2.2                     | $I^2C$ register tables                                        |   |

|    | 3.3                 | -                         | data from the IPQ $\mu$ C                                     |   |

|    | 3.3                 | 3.3.1                     | Content of status register                                    |   |

|    |                     |                           | -                                                             |   |

|    | 2.4                 | 3.3.2<br>Timing on        | Content of the following Read Registers                       |   |

|    | 3.4                 | Timing as                 | pects                                                         | , |

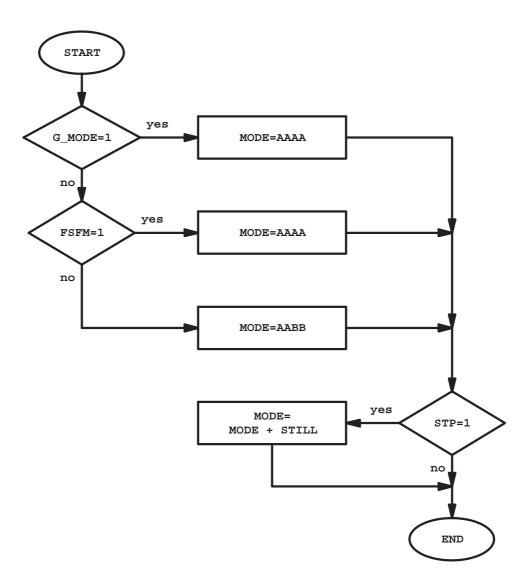

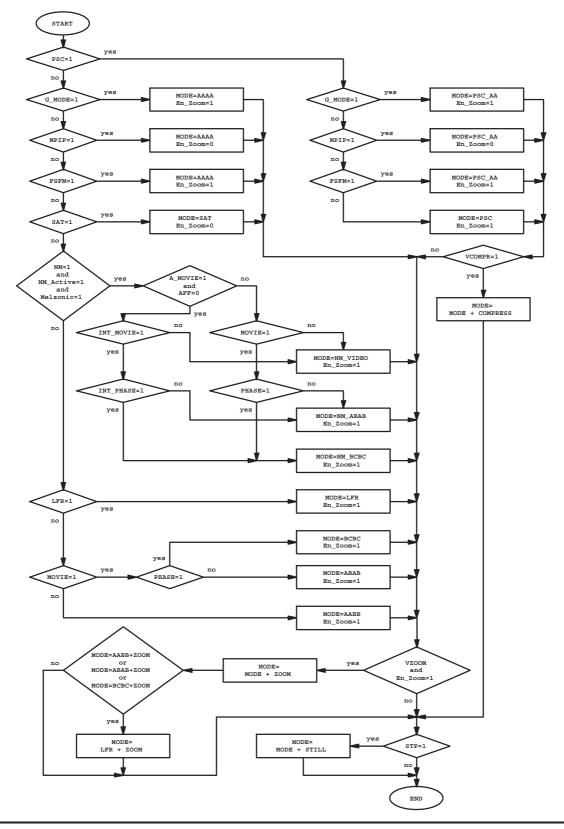

| 4. | Evalua              | ation of I <sup>2</sup> C | -bus register data                                            |   |

|    | 4.1                 | Field Men                 | nory Control Modes                                            |   |

|    |                     | 4.1.1                     | AABB Mode                                                     | , |

|    |                     | 4.1.2                     | LFR Mode                                                      | , |

|    |                     | 4.1.3                     | Natural Motion (Video and Movie)                              | , |

|    |                     | 4.1.4                     | ABAB Movie Mode                                               | 5 |

|    |                     | 4.1.5                     | Satellite Mode                                                | 5 |

|    |                     | 4.1.6                     | Progressive Scan Mode (PSC)                                   |   |

|    |                     | 4.1.7                     | Generator Mode (G_Mode)                                       |   |

|    |                     | 4.1.8                     | Auto Movie Detection routine                                  |   |

|    |                     |                           | Auto Movie Detection in the Melzonic concept                  |   |

|    |                     |                           | Auto Movie Detection in the Prozonic concept                  |   |

|    |                     | 4.1.9                     | Multi-PIP (MPIP)                                              |   |

|    |                     | 4.1.10                    | Forced Single Field Mode (FSFM)                               |   |

|    |                     | 4.1.11                    | Vertical Zoom                                                 |   |

|    |                     | 4.1.12                    | Vertical Compression                                          |   |

|    |                     | 4.1.12                    | Still Picture Mode                                            |   |

|    |                     | 4.1.14                    | Non-Interlace Mode                                            |   |

|    |                     | 4.1.15                    | INIT                                                          |   |

|    | 4.2                 |                           | of field memory control modes                                 |   |

|    | 4.2                 | 4.2.1                     | Single field memory concept                                   |   |

|    |                     | 4.2.1                     |                                                               |   |

|    | 4.2                 |                           | Two field memory concepts    38      v control commande    30 |   |

|    | 4.3                 |                           | y control commands                                            |   |

|    |                     | 4.3.1                     | Memory control of the SAA 4977 V1C                            |   |

|    |                     |                           | Acquisition Field Frequency selection (AFF)                   |   |

|    |                     |                           | HWE Delay                                                     | 1 |

4.4 4.5

# I2C-bus Register Specification for the SAA 4977 V1C

### User Manual HVS/UM9802

|         | VWE Delay                                       |

|---------|-------------------------------------------------|

|         | Blank Field Mode                                |

|         | Selection of the Colour Decoder Concept         |

|         | Select Field Recognition                        |

|         | Field length limit control                      |

|         | DAC blanking control                            |

|         | HDAV control                                    |

|         | HRE control                                     |

|         | HBLND control                                   |

|         | CLV control                                     |

|         | HWE control                                     |

|         | HDDEL control                                   |

|         | Field recognition control                       |

|         | HRA control                                     |

|         | HVA control                                     |

|         | HP control                                      |

| 4.3.2   | MELZONIC/PROZONIC control                       |

|         | Noise reduction                                 |

|         | Split Screen                                    |

|         | Selection of the Application Concept            |

|         | FILL control                                    |

|         | Direct control of the Natural Motion Parameters |

|         | BAD_LIMIT                                       |

|         | Reliability Threshold                           |

|         | Direct control of HOR_DEL register              |

|         | Vector Overlay                                  |

| 4.3.3   | Port Pin Control                                |

| 4.3.4   | Limeric control                                 |

| 4.3.5   | Datapath control.                               |

|         | Horizontal Compression                          |

|         | Screen fade                                     |

|         | Side panel control                              |

| •       | translator registers                            |

| SNERT i | nterface                                        |

## User Manual HVS/UM9802

#### 1. Introduction

The UM9705 V1.0 describes the I<sup>2</sup>C interface of the SAA 4977 V1C. The software of this BESIC version supports all the concepts described in the application notes AN97057 and AN 97071. This means it supports the single field concept, the PROZONIC concept and the MELZONIC concept.

#### 1.1 Definitions, Acronyms and Abbreviations

| AFF            | Acquisition field frequency                                      |

|----------------|------------------------------------------------------------------|

| BESIC          | SAA4977 V1C                                                      |

| HEX            | Hexadecimal                                                      |

| HOST interface | BESIC Interface towards 8051 microprocessor core                 |

| IIC            | Inter Integrated Circuit                                         |

| IPQCS          | Improved Picture Quality Control Software                        |

| ΙΡQ μC         | Improved Picture Quality slave microcontroller                   |

| LFR            | Line Flicker Reduction by median filtering                       |

| LIMERIC        | Line memory and Noise Reduction IC                               |

| MELZONIC       | Motion Estimation/compensation, Line flicker reduction, ZOom and |

|                | Noise reduction IC                                               |

| MPD            | Movie Phase Detection                                            |

| MPIP           | Multi picture in picture with external PIP processor             |

| NR             | Noise reduction (adaptive)                                       |

| PROZONIC       | PROgressive Scan, Zoom and Noise reduction IC                    |

| SCP            | Software Creation Process                                        |

| VDFL           | Vertical Deflection pulse (output of memory controller)          |

**Philips Semiconductors**

## I2C-bus Register Specification for the SAA 4977 V1C

| 1.2 | References                                                                                                   |

|-----|--------------------------------------------------------------------------------------------------------------|

| [1] | Philips Semiconductors Software Creation Process V1.0; Wilko van Asseldonk,<br>Marc de Smet; April 9th, 1996 |

| [2] | Tentative Device Specification for BESIC; 06.08.96; A. Kannengiesser                                         |

| [3] | Tentative Device Specification Control Part BESIC; 24.06.96; G. Stäcker,                                     |

|     | H. Waterholter                                                                                               |

| [4] | 80C51 microcontroller order form                                                                             |

| [5] | 80C51 microcontroller Core Specification V1.2; 22.02.96; P. Klapproth                                        |

| [6] | Datapath Control Register; 13.08.96; A. Kannengiesser                                                        |

| [7] | Application Note, MK8 Module, AN97057; H. Waterholter                                                        |

| [8] | Application Note, MK9 Module, AN97071; H. Waterholter                                                        |

| [9] | Software Creation Process, Nov. 18th 1997                                                                    |

#### 2. General

The IPQ  $\mu$ C receives register bytes via the I<sup>2</sup><sub>2</sub>C-bus from the master  $\mu$ C and sends itself 1 status byte plus following read registers whenever addressed with R/W = 1. The I<sup>2</sup>C register bytes received are written into RAM of the IPQ  $\mu$ C.

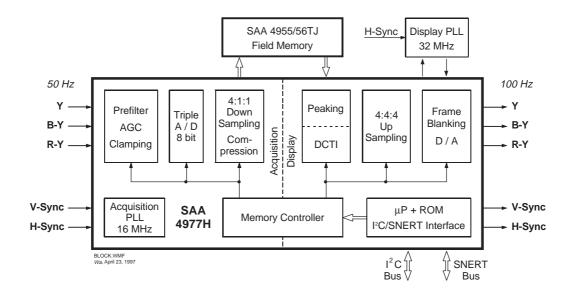

#### 2.1 Description of the different hardware concepts

The SAA 4977 is an IC which allows a very cost-effective design of scan converters. It contains an ADC with clamping function and gain control. The ADC is followed by a signal processing block providing a horizontal compression by the factors 1.17 and 1.33 for 14:9 and 16:9 applications. The data from the compression block is supplied to a field memory. The SAA 4977 also contains a memory controller based on the SAA 4952. An 8051 µ-controller core with ROM is implemented as well. The display datapath provides a high performance digital colour transient improvement and a luminance peaking. In the last block the digital display data are converted into analog signals.

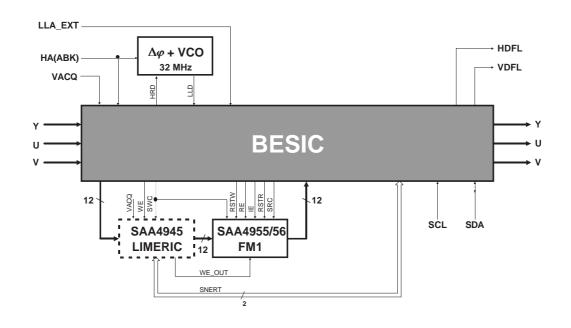

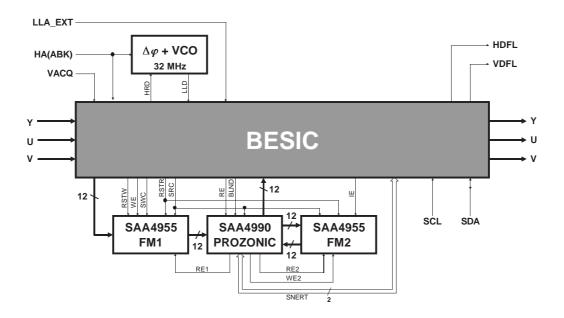

There are different hardware configurations which are supported by the SAA 4977. The low-cost versions only uses one field memory SAA 4955/56. Until the SAA 4956 is finalized the low-cost concept can be upgraded with the LIMERIC (SAA 4945). The mid-range concept is realized with two field memories (SAA 4955) and the PROZONIC (SAA 4990). This concept supports 100 Hz and progressive scan with line flicker reduction, vertical zoom and noise reduction. In the high-end concept the PROZONIC is replaced by the MELZONIC (SAA 4991). This concept provides a vectorbased motion compensation for a 100 Hz conversion free of motion effects.

## User Manual HVS/UM9802

#### 2.2 Block diagrams

2.2.1 SAA 4977 block diagram

2.2.2 Single field concept

.

### User Manual HVS/UM9802

#### 2.2.3 PROZONIC concept

2.2.4 MELZONIC concept

### User Manual HVS/UM9802

### 3. I<sup>2</sup>C-bus interface

#### 3.1 Definition of the interface

The interface of the IPQ  $\mu$ C is realized with a hardware I<sup>2</sup>C-bus.

The slave address of the IPQ  $\mu$ C is 68h:

Slave address = 0 1 1 0 1 0 0 R/W.

The IPQ  $\mu$ C can either act as a slave receiver or a slave transmitter. In the slave receiver mode the IPQ  $\mu$ C reads I<sup>2</sup>C register data bytes from the main controller which then acts as a master transmitter. In the slave transmitter mode the IPQ  $\mu$ C sends status information to the main  $\mu$ C which works as a master receiver reading the byte information.

#### 3.2 Sending data to the IPQ µC

#### 3.2.1 I<sup>2</sup>C transmission protocol

The transmission protocol has the following format:

| Start | Slave<br>address 68h | Ack | Subad-<br>dress | Ack | REG1 | Ack |  | Ack | REGx | Ack | Stop | ] |

|-------|----------------------|-----|-----------------|-----|------|-----|--|-----|------|-----|------|---|

|-------|----------------------|-----|-----------------|-----|------|-----|--|-----|------|-----|------|---|

After having addressed the IPQ  $\mu$ C with its slave address the master  $\mu$ C transmits the subaddress plus following register bytes over the I<sup>2</sup>C-bus. The number of register bytes which are transmitted after the transmission of the subaddress is free choosable. It is possible to transmit just one single register byte after having sent the slaveaddress plus subaddress (3 bytes package).

The IPQ  $\mu$ C acknowledges always all register bytes independent of their contents. If the master  $\mu$ C transmits more than the maximum number of register bytes, the slave  $\mu$ C will acknowledge the following bytes, but will not store them in the internal RAM.

Subaddresses starting from 30h onwards indicate, that datapath control registers are to be serviced.

## 3.2.2 I<sup>2</sup>C register tables

[Default hex values in brackets]

| Bit | Name                                                                                  | Function                                                                                                                                                                                              |  |  |  |  |  |

|-----|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0   | PSC                                                                                   | 0: Progressive scan mode off<br>1: Progressive scan mode on                                                                                                                                           |  |  |  |  |  |

| 1   | G_MODE 0: Generator mode off<br>1: Generator mode on (312,5 lines / field constantly) |                                                                                                                                                                                                       |  |  |  |  |  |

| 2   | FSFM                                                                                  | 0: Forced Single Field mode off<br>1: Forced Single Field mode on                                                                                                                                     |  |  |  |  |  |

| 3   | SAT                                                                                   | 0: Satellite mode off<br>1: Satellite mode on (A*A*B*B*)                                                                                                                                              |  |  |  |  |  |

| 4   | A_MOVIE                                                                               | 0: movie detection disabled<br>1: automatic movie source detection activated; in case a movie mode is<br>detected, a movie will be processed (MOVIE, MOVIE_PHASE are readable via<br>STATUS register) |  |  |  |  |  |

| 5   | NM                                                                                    | 0: Natural Motion mode off<br>1: Natural Motion mode on                                                                                                                                               |  |  |  |  |  |

| 6   | LFR                                                                                   | 0: Line Flicker Reduction mode off<br>1: Line Flicker Reduction mode on                                                                                                                               |  |  |  |  |  |

| 7   | reserved                                                                              |                                                                                                                                                                                                       |  |  |  |  |  |

## TABLE 2 I<sup>2</sup>C Subaddress 01 hex [Default: 00 hex]

| Bit | Name  | Function                 |                |                                             |  |  |  |  |

|-----|-------|--------------------------|----------------|---------------------------------------------|--|--|--|--|

| 0   | MOVIE | 0: Forced Movie mode off |                |                                             |  |  |  |  |

| 0   |       | 1: Forced Movie mode on  |                |                                             |  |  |  |  |

|     |       |                          |                | set in combination with MOVIE:              |  |  |  |  |

| 1   | PHASE | 0: normal (ABAB)         |                |                                             |  |  |  |  |

|     |       | 1: 180° pha              | se shift (BCE  | 3C)                                         |  |  |  |  |

|     |       | still picture i          | mode:          |                                             |  |  |  |  |

| 2   | STP   | 0: off                   |                |                                             |  |  |  |  |

|     |       | 1: on (one f             | ield out of AA | ABB, full frame median filtered out of LFR) |  |  |  |  |

|     |       | •                        | ield frequend  | cy (50/60 Hz):                              |  |  |  |  |

| 3   | AFF   | 0: 50 Hz                 |                |                                             |  |  |  |  |

|     |       | 1: 60 Hz                 |                |                                             |  |  |  |  |

| 4   | COMP0 | 0: compression off       |                |                                             |  |  |  |  |

| т   |       | 1: compression on        |                |                                             |  |  |  |  |

| 5   | COMP1 | 0: 14:9 compression mode |                |                                             |  |  |  |  |

| 5   |       | 1: 16:9 compression mode |                |                                             |  |  |  |  |

| 6   | PP0   | picture posi             | tion bit 0     |                                             |  |  |  |  |

| 7   | PP1   | picture posi             | tion bit 1     |                                             |  |  |  |  |

|     |       | PP1                      | PP0            | picture position                            |  |  |  |  |

|     |       | 0                        | 0              | centre                                      |  |  |  |  |

|     |       | 0                        | 1              | max. left                                   |  |  |  |  |

|     |       | 1 0 max. right           |                |                                             |  |  |  |  |

User Manual HVS/UM9802

### User Manual HVS/UM9802

| Bit | Name     | Function                                                    |         |          |    |                   |  |  |

|-----|----------|-------------------------------------------------------------|---------|----------|----|-------------------|--|--|

| 0   | VZOOM_0  | Vertical zoom bit 0                                         |         |          |    |                   |  |  |

| 1   | VZOOM_1  | Verti                                                       | cal zoo | om bit ' | 1  |                   |  |  |

| 2   | VZOOM_2  | Vertio                                                      | cal zoo | om bit 2 | 2  |                   |  |  |

| 3   | VZOOM_3  | Vertio                                                      | cal zoo | om bit : | 3  |                   |  |  |

|     |          | V3                                                          | V2      | V1       | V0 | Conversion factor |  |  |

|     |          | 0                                                           | 0       | 0        | 0  | no zoom           |  |  |

|     |          | 0                                                           | 0       | 0        | 1  | 1,06*)            |  |  |

|     |          | 0                                                           | 0       | 1        | 0  | 1,1               |  |  |

|     |          | 0                                                           | 0       | 1        | 1  | 1,15*)            |  |  |

|     |          | 0                                                           | 1       | 0        | 0  | 1,2*)             |  |  |

|     |          | 0                                                           | 1       | 0        | 1  | 1,25              |  |  |

|     |          | 0                                                           | 1       | 1        | 0  | 1,3*)             |  |  |

|     |          | 0                                                           | 0 1 1 1 |          |    | 1,33              |  |  |

|     |          | 1                                                           | 0       | 0        | 0  | 1,5               |  |  |

|     |          | 1                                                           | 0       | 0        | 1  | reserved          |  |  |

|     |          |                                                             |         |          |    | reserved          |  |  |

|     |          | 1                                                           | 1       | 1        | 1  | reserved          |  |  |

| 4   | VCOMPR   | Vertical compress                                           |         |          |    |                   |  |  |

| 5   | reserved |                                                             |         |          |    |                   |  |  |

| 6   | reserved |                                                             |         |          |    |                   |  |  |

| 7   | INIT     | initialize SAA 4977 V1C, PROZONIC/MELZONIC: 0 = off, 1 = on |         |          |    |                   |  |  |

## TABLE 3 I<sup>2</sup>C Subaddress 02 hex (VZOOM) [Default: 00 hex]

\*) these zoom-factors are allowed only in the MELZONIC IPQ concept in the LFR or FSFM mode or in the PROZONIC IPQ concept in the PSC mode

| Bit | Name     | Function                                        |

|-----|----------|-------------------------------------------------|

| 0   | POS0     | PIP position bit 0                              |

| 1   | POS1     | PIP position bit 1                              |

| 2   | POS2     | PIP position bit 2                              |

| 3   | POS3     | PIP position bit 3                              |

| 4   | reserved |                                                 |

| 5   | NPIP     | number of PIP's<br>0: 3x3 PIP's<br>1: 4x3 PIP's |

| 6   | MPIP     | 0: Multi-PIP off<br>1: Multi-PIP on             |

| 7   | SPIP     | NTSC PIP:<br>0: 50 Hz PIP<br>1: 60 Hz PIP       |

| Bit | Name   | Function                                                                                                                                                |         |                 |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------|

| 0   | NR0    | noise reduction bit 0                                                                                                                                   |         |                 |

| 1   | NR1    | noise reduction bit 1                                                                                                                                   |         |                 |

|     |        | NR1                                                                                                                                                     | NR0     | noise reduction |

|     |        | 0                                                                                                                                                       | 0       | off             |

|     |        | 0                                                                                                                                                       | 1       | low             |

|     |        | 1                                                                                                                                                       | 0       | middle          |

|     |        | 1                                                                                                                                                       | 1       | high            |

| 2   | SPS0   | split screen                                                                                                                                            | bit 0   |                 |

| 3   | SPS1   | split screen bit 1                                                                                                                                      |         |                 |

|     |        | SPS1                                                                                                                                                    | SPS0    | split screen    |

|     |        | 0                                                                                                                                                       | Х       | off             |

|     |        | 1                                                                                                                                                       | 0       | horizontal      |

|     |        | 1                                                                                                                                                       | 1       | vertical        |

| 4   | SCF0   | screen fade                                                                                                                                             | e bit 0 |                 |

| 5   | SCF1   | screen fade bit 1                                                                                                                                       |         |                 |

|     |        | SCF1                                                                                                                                                    | SCF0    | screen fade     |

|     |        | 0                                                                                                                                                       | Х       | off             |

|     |        | 1                                                                                                                                                       | 0       | fade in         |

|     |        | 1                                                                                                                                                       | 1       | fade out        |

| 6   | NR_INT | <ul><li>0: normal mode</li><li>1: noise reduction processing (bits 1,2) is cancelled each second for the duration of one single display field</li></ul> |         |                 |

| 7   | PSC_DR | 0: normal mode<br>1: in PROGRESSIVE SCAN mode the display will run in interlace mode                                                                    |         |                 |

## TABLE 5 I<sup>2</sup>C Subaddress 04 hex (NR, SCREEN FADE) [Default: 01 hex]

## TABLE 6 I<sup>2</sup>C Subaddress 05 hex (HWE DELAY) [Default: 20 hex]

| Bit | Name   | Function (clock accuracy)               |

|-----|--------|-----------------------------------------|

| 0   | HWE1F0 | HWE1 fine delay offset to default, bit0 |

| 1   | HWE1F1 | HWE1 fine delay offset to default, bit1 |

| 2   | HWE1F2 | HWE1 fine delay offset to default, bit2 |

| 3   | HWE1F3 | HWE1 fine delay offset to default, bit3 |

| 4   | HWE1F4 | HWE1 fine delay offset to default, bit4 |

| 5   | HWE1F5 | HWE1 fine delay offset to default, bit5 |

| 6   | HWE1F6 | HWE1 fine delay offset to default, bit6 |

| 7   | HWE1F7 | HWE1 fine delay offset to default, bit7 |

## TABLE 7 I<sup>2</sup>C Subaddress 06 hex (VWE DELAY) [Default: 00 hex]

| Bit | Name     | Function (line accuracy)                                                                                                |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------|

| 0   | VWE1D0   | VWE1 delay bit 0                                                                                                        |

| 1   | VWE1D1   | VWE1 delay bit 1                                                                                                        |

| 2   | VWE1D2   | VWE1 delay bit 2                                                                                                        |

| 3   | VWE1D3   | VWE1 delay bit 3                                                                                                        |

| 4   | VWE1D4   | VWE1 delay bit 4                                                                                                        |

| 5   | VWE1D5   | VWE1 delay bit 5                                                                                                        |

| 6   | VWE1D6   | VWE1 delay bit 6                                                                                                        |

| 7   | A_VSHIFT | 0: VSHIFT for VZOOM via I <sup>2</sup> C Subaddress 06 hex<br>1: VSHIFT for ZOOM is done automatically in the FSFM mode |

## TABLE 8 I<sup>2</sup>C Subaddress 07 hex (BLANK FIELDS) [Default: 80 hex]

| Bit | Name     | Function          |                                                                       |                                                                                                                   |  |

|-----|----------|-------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| 0   | BLANK_F0 | Blank field 0     |                                                                       |                                                                                                                   |  |

| 1   | BLANK_F1 | Blank field       | 1                                                                     |                                                                                                                   |  |

| 2   | BLANK_F2 | Blank field       | 2                                                                     |                                                                                                                   |  |

| 3   | BLANK_F3 | Blank field       | 3                                                                     |                                                                                                                   |  |

| 4   | DCD      | •                 | 0: analog colour decoder concept<br>1: digital colour decoder concept |                                                                                                                   |  |

| 5   | CON0     | IPQ concept bit 0 |                                                                       |                                                                                                                   |  |

| 6   | CON1     | IPQ concept bit 1 |                                                                       |                                                                                                                   |  |

|     |          | CON1              | CON0                                                                  | IPQ concept                                                                                                       |  |

|     |          | 0                 | 0                                                                     | Single field concept                                                                                              |  |

|     |          | 0                 | 1                                                                     | PROZONIC                                                                                                          |  |

|     |          | 1                 | X                                                                     | MELZONIC                                                                                                          |  |

|     |          | 0: SFR (VA        | MSB)=0                                                                |                                                                                                                   |  |

| 7   | SFR      | This contro       | I bit is not ac                                                       | n SFR (VAMSB) = 1<br>tive if the PROZONIC hardware concept is selected and<br>processing is LFR with A_MOVIE set! |  |

## TABLE 9 I<sup>2</sup>C Subaddress 08 hex (PORT SETTINGS) [Default: FF hex]

| Bit | Name     | Function                                       |

|-----|----------|------------------------------------------------|

| 0   | P11      | 0: clear port bit P1.1<br>1: set port bit P1.1 |

| 1   | P12      | 0: clear port bit P1.2<br>1: set port bit P1.2 |

| 2   | P13      | 0: clear port bit P1.3<br>1: set port bit P1.3 |

| 3   | P14      | 0: clear port bit P1.4<br>1: set port bit P1.4 |

| 4   | P15      | 0: clear port bit P1.5<br>1: set port bit P1.5 |

| 5   | reserved |                                                |

| 6   | reserved |                                                |

| 7   | reserved |                                                |

#### TABLE 10 I<sup>2</sup>C Subaddress 09 hex ([Default: 00 hex])

| Bit | Name            | Function                                                                                                                                      |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | NM_CTL          | 0: normal mode<br>1: bad limit taken from I <sup>2</sup> C Subaddress 29h<br>reliability threshold taken from I <sup>2</sup> C Subaddress 2Ah |

| 1   | SET_HOR_<br>DEL | 0: normal mode<br>1: take HOR_DELAYS setting from I <sup>2</sup> C Subaddress 26h                                                             |

| 2   | SET_NR          | 0: normal mode<br>1: direct noise reduction control via I <sup>2</sup> C Subaddresses 1Fh25h                                                  |

| 3   | FILL            | 0: normal mode<br>1: fill screen with colour selected via I <sup>2</sup> C Subaddress 27h and 28h                                             |

| 4   | SET_SIDEP       | 0: normal mode<br>1: set SIDEPANEL_START and SIDEPANEL_STOP values direct via I <sup>2</sup> C Subad-<br>dresses 3Dh and 3Eh                  |

| 5   | VEC_OVL         | 0: normal mode<br>1: vector overlay active                                                                                                    |

| 6   | reserved        |                                                                                                                                               |

| 7   | SET_VBDA        | 0: normal mode<br>1: set VBDASTA/STO values direct via I <sup>2</sup> C Subaddresses 0Bh, 0Ch and 0Dh                                         |

### User Manual HVS/UM9802

#### TABLE 11 I<sup>2</sup>C Subaddress 0A hex [Default: 00 hex]

| Bit | Name      | Function                                                                                                                      |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------|

| 0   | SET_HDAV  | 0: normal mode<br>1: set HDAVSTA/STO values direct via I <sup>2</sup> C Subaddresses 0Eh, 0Fh and 16h                         |

| 1   | SET_HBDA  | 0: normal mode<br>1: set HBDASTA/STO values direct via I <sup>2</sup> C Subaddresses 10h, 11h and 16h                         |

| 2   | SET_HRE   | 0: normal mode<br>1: set HRESTA/STO values direct via I <sup>2</sup> C Subaddresses 12h, 13h and 16h                          |

| 3   | SET_HBLND | 0: normal mode<br>1: set HBLNDSTA/STO values direct via I <sup>2</sup> C Subaddresses 14h, 15h and 16h                        |

| 4   | SET_HDDEL | 0: normal mode<br>1: set HDDEL value direct via I <sup>2</sup> C Subaddress 17h                                               |

| 5   | SET_CLV   | 0: normal mode<br>1: set CLVSTA/STO values direct via I <sup>2</sup> C Subaddresses 18h and 19h                               |

| 6   | SET_HWE   | 0: normal mode<br>1: set HWESTA/STO values direct via I <sup>2</sup> C Subaddresses 1Ah, 1Bh and 0Dh                          |

| 7   | SET_FRG   | 0: normal mode<br>1: set HRASTO, HVA_1, HVA_2 and HP1 values direct via I <sup>2</sup> C Subaddresses 1Ch,<br>1Dh,1Eh and 2Bh |

## TABLE 12 I<sup>2</sup>C Subaddress 0B hex (VBDASTA) [Default: 15 hex]

| Bit    | Name    | Function                                 |

|--------|---------|------------------------------------------|

| 0<br>7 | VBDASTA | direct memory controller register access |

## TABLE 13 I<sup>2</sup>C Subaddress 0C hex (VBDASTO) [Default: 31 hex]

| Bit    | Name    | Function                                 |

|--------|---------|------------------------------------------|

| 0<br>7 | VBDASTO | direct memory controller register access |

## TABLE 14 I<sup>2</sup>C Subaddress 0D hex (MSBREG1) [Default: 0A hex]

| Bit    | Name            | Function                                 |

|--------|-----------------|------------------------------------------|

| 0      | MSB_<br>VBDASTA | direct memory controller register access |

| 1      | MSB_<br>VBDASTO | direct memory controller register access |

| 2      | MSB_<br>HWESTA  | direct memory controller register access |

| 3      | MSB_<br>HWESTO  | direct memory controller register access |

| 4<br>7 | reserved        |                                          |

#### TABLE 15 I<sup>2</sup>C Subaddress 0E hex (HDAVSTA) [Default: 28 hex]

| Bit    | Name    | Function                                 |

|--------|---------|------------------------------------------|

| 0<br>7 | HDAVSTA | direct memory controller register access |

## TABLE 16 I<sup>2</sup>C Subaddress 0F hex (HDAVSTO) [Default: 00 hex]

| Bit    | Name    | Function                                 |  |

|--------|---------|------------------------------------------|--|

| 0<br>7 | HDAVSTO | direct memory controller register access |  |

### TABLE 17 I<sup>2</sup>C Subaddress 10 hex (HBDASTA) [Default: 55 hex]

| Bit    | Name    | Function                                 |

|--------|---------|------------------------------------------|

| 0<br>7 | HBDASTA | direct memory controller register access |

## TABLE 18 I<sup>2</sup>C Subaddress 11 hex (HBDASTO) [Default: EE hex]

| Bit    | Name    | Function                                 |

|--------|---------|------------------------------------------|

| 0<br>7 | HBDASTO | direct memory controller register access |

#### TABLE 19 I<sup>2</sup>C Subaddress 12 hex (HRESTA) [Default: 3A hex]

| Bit    | Name   | Function                                 |

|--------|--------|------------------------------------------|

| 0<br>7 | HRESTA | direct memory controller register access |

#### TABLE 20 I<sup>2</sup>C Subaddress 13 hex (HRESTO) [Default: DE hex]

| Bit    | Name   | Function                                 |

|--------|--------|------------------------------------------|

| 0<br>7 | HRESTO | direct memory controller register access |

### TABLE 21 I<sup>2</sup>C Subaddress 14 hex (HBLNDSTA) [Default: 00 hex]

| Bit    | Name     | Function                                 |

|--------|----------|------------------------------------------|

| 0<br>7 | HBLNDSTA | direct memory controller register access |

## TABLE 22 I<sup>2</sup>C Subaddress 15 hex (HBLNDSTO) [Default: 00 hex]

| Bit    | Name     | Function                                 |

|--------|----------|------------------------------------------|

| 0<br>7 | HBLNDSTO | direct memory controller register access |

### User Manual HVS/UM9802

#### TABLE 23 I<sup>2</sup>C Subaddress 16 hex (MSB REG2) [Default: 2A hex]

| Bit | Name             | Function                                 |

|-----|------------------|------------------------------------------|

| 0   | MSB_ HDAVSTA     | direct memory controller register access |

| 1   | MSB_ HDAVSTO     | direct memory controller register access |

| 2   | MSB_ HBDASTA     | direct memory controller register access |

| 3   | MSB_ HBDASTO     | direct memory controller register access |

| 4   | HRESTA           | direct memory controller register access |

| 5   | HRESTO           | direct memory controller register access |

| 6   | MSB_<br>HBLNDSTA | direct memory controller register access |

| 7   | MSB_<br>HBLNDSTO | direct memory controller register access |

### TABLE 24 I<sup>2</sup>C Subaddress 17 hex (HDDEL) [Default: 00 hex]

| Bit    | Name     | Function            |

|--------|----------|---------------------|

| 0      |          | fine delay of HDAV  |

| 1      | HDDEL    | fine delay of HBDA  |

| 2      |          | fine delay of HRE   |

| 3      |          | fine delay of HBLND |

| 4<br>7 | reserved |                     |

#### TABLE 25 I<sup>2</sup>C Subaddress 18 hex (CLVSTA) [Default: 00 hex]

| Bit    | Name   | Function                                 |

|--------|--------|------------------------------------------|

| 0<br>7 | CLVSTA | direct memory controller register access |

### TABLE 26 I<sup>2</sup>C Subaddress 19 hex (CLVSTO) [Default: 09 hex]

| Bit    | Name   | Function                                 |

|--------|--------|------------------------------------------|

| 0<br>7 | CLVSTO | direct memory controller register access |

### TABLE 27 I<sup>2</sup>C Subaddress 1A hex (HWESTA) [Default: 2C hex]

| Bit    | Name   | Function                                 |

|--------|--------|------------------------------------------|

| 0<br>7 | HWESTA | direct memory controller register access |

### TABLE 28 I<sup>2</sup>C Subaddress 1B hex (HWESTO) [Default: D0 hex]

| Bit    | Name   | Function                                 |

|--------|--------|------------------------------------------|

| 0<br>7 | HWESTO | direct memory controller register access |

## TABLE 29 I<sup>2</sup>C Subaddress 1C hex (HRASTO) [Default: 80 hex]

| Bit    | Name   | unction                                  |  |

|--------|--------|------------------------------------------|--|

| 0<br>7 | HRASTO | direct memory controller register access |  |

## TABLE 30 I<sup>2</sup>C Subaddress 1D hex (HVA\_1) [Default: 28 hex]

| Bit    | Name  | Function                                 |  |

|--------|-------|------------------------------------------|--|

| 0<br>7 | HVA_1 | direct memory controller register access |  |

### TABLE 31 I<sup>2</sup>C Subaddress 1E hex (HVA\_2) [Default: A8 hex]

| Bit    | Name  | Function                                 |  |

|--------|-------|------------------------------------------|--|

| 0<br>7 | HVA_2 | direct memory controller register access |  |

### TABLE 32 I<sup>2</sup>C Subaddress 1F...25 hex

| Subaddress |           |                                                                                                        |

|------------|-----------|--------------------------------------------------------------------------------------------------------|

| (hex)      | Name      | Function                                                                                               |

| 1F         | KSTEP01   | direct PROZONIC/MELZONIC register access (default: 34 hex)                                             |

| 20         | KSTEP23   | direct PROZONIC/MELZONIC register access (default: 34 hex)                                             |

| 21         | KSTEP45   | direct PROZONIC/MELZONIC register access (default: 34 hex)                                             |

| 22         | KSTEP67   | direct PROZONIC/MELZONIC register access (default: 34 hex)                                             |

| 23         | KFIXED    | direct PROZONIC/MELZONIC register access (default: 8F hex)                                             |

| 24         | TFILTER12 | direct PROZONIC/MELZONIC register access (default: 55 hex)                                             |

| 25         | DEF       | direct PROZONIC register access (default: 09 hex)<br>direct MELZONIC register access (default: 00 hex) |

## TABLE 33 I<sup>2</sup>C Subaddress 26 hex (HOR\_DELAYS) [Default: 28 hex]

| Bit    | Name           | Function                                 |  |

|--------|----------------|------------------------------------------|--|

| 0<br>7 | HOR_<br>DELAYS | direct PROZONIC/MELZONIC register access |  |

### TABLE 34 I<sup>2</sup>C Subaddress 27 hex (FIXCOL\_Y) [Default: 16 hex]

| Bit    | it Name Function |                                 |

|--------|------------------|---------------------------------|

| 0<br>7 | FIXCOL_Y         | direct MELZONIC register access |

#### TABLE 35 I<sup>2</sup>C Subaddress 28 hex (FIXCOL\_UV) [Default: 08 hex]

| Bit    | Name      | Function                        |  |

|--------|-----------|---------------------------------|--|

| 0<br>7 | FIXCOL_UV | direct MELZONIC register access |  |

#### TABLE 36 I<sup>2</sup>C Subaddress 29 hex (BAD\_LIMIT) [Default: 40 hex]

| Bit    | Name      | Function                                                                             |  |

|--------|-----------|--------------------------------------------------------------------------------------|--|

| 0<br>7 | BAD_LIMIT | direct BAD_LIMIT setting<br>(Software threshold for NR_BAD_RANGES, MELZONIC control) |  |

## TABLE 37 I<sup>2</sup>C Subaddress 2A hex (RELIABILITY\_SEL) [Default: 30 hex]

| Bit    | Name            | Function                        |  |

|--------|-----------------|---------------------------------|--|

| 0<br>7 | RELIABILITY_SEL | direct MELZONIC register access |  |

### TABLE 38 I<sup>2</sup>C Subaddress 2B hex (HP1) [Default: A8 hex]

| Bit    | Name | Function                                                                                                                                                                            |  |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0<br>7 | HP1  | direct memory controller register access;<br>the control values of the pulses HP2, HP3 and HP4 are automatically adapted that<br>the distance of the 4 HP pulses is 40 Hex (=16 us) |  |

#### TABLE 39 I<sup>2</sup>C Subaddress 2C hex (LIMERIC1) [Default: 00 hex]

| Bit | Name     | Function                                                          | Function                     |            |                         |  |

|-----|----------|-------------------------------------------------------------------|------------------------------|------------|-------------------------|--|

| 0   | L_NR0    | LIMERIC                                                           | LIMERIC Noise Reduction bit0 |            |                         |  |

| 1   | L_NR1    | LIMERIC                                                           | Noise Redu                   | ction bit1 |                         |  |

| 2   | L_NR2    | LIMERIC                                                           | Noise Redu                   | ction bit2 |                         |  |

|     |          | L_NR0                                                             | L_NR1                        | L_NR2      |                         |  |

|     |          | 0                                                                 | 0                            | 0          | Noise-Reduction off     |  |

|     |          | 0                                                                 | 0                            | 1          | Noise-Reduction low     |  |

|     |          | 0                                                                 | 1                            | 0          | Noise-Reduction middle  |  |

|     |          | 0                                                                 | 1                            | 1          | Noise-Reduction high    |  |

|     |          | 1                                                                 | 0                            | 0          | Noise-Reduction highest |  |

| 3   | DEM      | 0: normal mode                                                    |                              |            |                         |  |

| 9   |          | 1: demo m                                                         | node                         |            |                         |  |

| 4   | WES      | 0: normal mode                                                    |                              |            |                         |  |

| т   | WEG      | 1: shift write enable for one clock                               |                              |            |                         |  |

| 5   | EX_THR   | 0: internal threshold                                             |                              |            |                         |  |

| Ŭ   |          | 1: set threshold value direct via I <sup>2</sup> C Subaddress 2Dh |                              |            |                         |  |

| 6   | reserved |                                                                   |                              |            |                         |  |

| 7   | reserved |                                                                   |                              |            |                         |  |

## TABLE 40 I<sup>2</sup>C Subaddress 2D hex (LIMERIC2) [Default: 00 hex]

| Bit    | Name | unction                        |  |

|--------|------|--------------------------------|--|

| 0<br>7 | NTHR | direct LIMERIC register access |  |

#### TABLE 41 I<sup>2</sup>C Subaddress 2E hex (LIMERIC3) [Default: 0F hex]

| Bit    | Name | Function                       |  |  |  |  |  |

|--------|------|--------------------------------|--|--|--|--|--|

| 0<br>7 | WVAL | direct LIMERIC register access |  |  |  |  |  |

#### I2C Translator Registers

#### TABLE 42 I<sup>2</sup>C Translator Subaddress 30 hex (ACQ\_0) [Default: 66 hex]

| Bit    | Name  | Host<br>Address | Default | Function                                                          |

|--------|-------|-----------------|---------|-------------------------------------------------------------------|

| 0<br>7 | AGC_Y | 150 hex         | hh hex  | AGC gain for the Y channel (2's complement rel 0dB): upper 8 bits |

## TABLE 43 I<sup>2</sup>C Translator Subaddress 31 hex (ACQ\_1) [Default: 90 hex]

| Bit    | Name   | Host<br>Address | Default | Function                                                                |

|--------|--------|-----------------|---------|-------------------------------------------------------------------------|

| 0<br>7 | AGC_UV | 151 hex         | 90 hex  | AGC gain for the U and V channel (2's complement rel 0dB): upper 8 bits |

#### TABLE 44 I<sup>2</sup>C Translator Subaddress 32 hex (ACQ\_2) [Default: 00 hex]

|        |            | Host     |         |                              |

|--------|------------|----------|---------|------------------------------|

| Bit    | Name       | Address  | Default | Function                     |

| 0      | AGC_Y_LSB  |          |         | AGC gain for Y channel LSB   |

| 1      | AGC_UV_LSB |          |         | AGC gain for UV channel LSB  |

| 2      | standby_f  | 152 hex  | 00 hex  | 1: frontend in stand-by mode |

| 3      | aaf_bypass | 102 1102 |         | 1: bypass for prefilter      |

| 4<br>7 | reserved   |          |         |                              |

#### TABLE 45 I<sup>2</sup>C Translator Subaddress 33 hex (ACQ\_3) [Default: 00 hex]

| Bit | Name             | Host<br>Address | Default | Function                                           |       |                                        |  |  |

|-----|------------------|-----------------|---------|----------------------------------------------------|-------|----------------------------------------|--|--|

| ы   | Name             | Address         | Delault | Func                                               | lion  |                                        |  |  |

|     |                  |                 |         | Bit1                                               | Bit 0 | UV clamp mode                          |  |  |

| 0   |                  |                 |         | 0                                                  | 0     | auto                                   |  |  |

| 0   | UVclcorrect_mode |                 | 00      | 0                                                  | 1     | fixed                                  |  |  |

|     |                  |                 |         | 1                                                  | 0     | keep                                   |  |  |

|     |                  | 153 hex         |         | 1                                                  | 1     | -                                      |  |  |

| 2   | Uclcorrect_      |                 | 000     | fixed                                              | value | clamp corr. U channel (2's complement) |  |  |

| 4   | fval             |                 | 000     |                                                    |       |                                        |  |  |

| 5   | Vclcorrect_      |                 | 000     | fixed value clamp corr. V channel (2's complement) |       |                                        |  |  |

| 7   | fval             |                 | 000     | fixed value clamp corr. V channel (2's complement) |       |                                        |  |  |

### User Manual HVS/UM9802

|        |          | Host     |         |          |      |                                      |  |  |  |

|--------|----------|----------|---------|----------|------|--------------------------------------|--|--|--|

| Bit    | Name     | Address  | Default | Function |      |                                      |  |  |  |

|        |          |          |         | Bit1     | Bit0 | UV coring level                      |  |  |  |

|        |          |          |         | 0        | 0    | 0                                    |  |  |  |

| 0      | UVcoring |          | 00      | 0        | 1    | +/- 0,5                              |  |  |  |

| 1      |          |          |         | 1        | 0    | +/- 1                                |  |  |  |

|        |          |          |         | 1        | 1    | +/- 2                                |  |  |  |

| 2      | reserved |          | 0       |          | •    |                                      |  |  |  |

| 3      | reserved | 154 hex  | 0       |          |      |                                      |  |  |  |

|        |          | 134 1167 |         | Bit1     | Bit0 | vertical filtering of measured clamp |  |  |  |

| 4      |          |          |         | 0        | 0    |                                      |  |  |  |

| 4<br>5 | UVcl_tau |          | 11      | 0        | 1    |                                      |  |  |  |

| J      |          |          |         | 1        | 0    |                                      |  |  |  |

|        |          |          |         | 1        | 1    |                                      |  |  |  |

| 6      | reserved | ]        | 0       |          |      |                                      |  |  |  |

| 7      | reserved |          | 0       |          |      |                                      |  |  |  |

## TABLE 46 I<sup>2</sup>C Translator Subaddress 34 hex (ACQ\_4) [Default: 30 hex]

#### TABLE 47 I<sup>2</sup>C Translator Subaddress 35 hex (ACQ\_5) [Default: 0A hex]

|          |           | Host    |         |                                           |      |         |                  |  |

|----------|-----------|---------|---------|-------------------------------------------|------|---------|------------------|--|

| Bit      | Name      | Address | Default | Function                                  |      |         |                  |  |

|          |           |         |         | Bit2                                      | Bit1 | Bit0    | variable Y-delay |  |

|          |           |         |         | 0                                         | 0    | 0       | -4               |  |

|          |           |         |         | 0                                         | 0    | 1       | -3               |  |

|          |           |         |         | 0                                         | 1    | 0       | -2               |  |

| 0<br>2   | Ydelay_f  |         | 010     | 0                                         | 1    | 1       | -1               |  |

| 2        |           |         |         | 1                                         | 0    | 0       | 0                |  |

|          |           | 155 hex |         | 1                                         | 0    | 1       | 1                |  |

|          |           |         |         | 1                                         | 1    | 0       | 2                |  |

|          |           |         |         | 1                                         | 1    | 1       | 3                |  |

|          |           | 100 Hex |         | Bit1                                      | Bit0 | overle  | bad threshold    |  |

| 2        |           |         |         | 0                                         | 0    | 216     |                  |  |

| 3<br>4   | overl_thr |         | 01      | 0                                         | 1    | 224     |                  |  |

| <b>–</b> |           |         |         | 1                                         | 0    | 232     |                  |  |

|          |           | -       |         | 1                                         | 1    | 240     |                  |  |

| 5        | fill_mem  |         | 0       | 0: standard mode, video data from the ADC |      |         |                  |  |

| 5        |           |         | 0       | 1: fill                                   | memo | ry with | constant value   |  |

| 6        | reserved  | 0       | 0       |                                           |      |         |                  |  |

| 7        | reserved  |         | 0       |                                           |      |         |                  |  |

### User Manual HVS/UM9802

| Bit    | Name               | Host    | Default | Function                          |      |      |           |  |

|--------|--------------------|---------|---------|-----------------------------------|------|------|-----------|--|

| DI     | Name               | Address | Default |                                   |      |      |           |  |

|        |                    |         |         | Bit2                              | Bit1 | Bit0 | DCTI gain |  |

|        |                    |         |         | 0                                 | 0    | 0    | 0         |  |

|        |                    |         |         | 0                                 | 0    | 1    | 1         |  |

|        |                    |         |         | 0                                 | 1    | 0    | 2         |  |

| 0<br>2 | dcti_gain          | 1D1 hex | 010     | 0                                 | 1    | 1    | 3         |  |

| 2      |                    |         |         | 1                                 | 0    | 0    | 4         |  |

|        |                    |         |         | 1                                 | 0    | 1    | 5         |  |

|        |                    |         |         | 1                                 | 1    | 0    | 6         |  |

|        |                    |         |         | 1                                 | 1    | 1    | 7         |  |

| 3<br>6 | dcti_<br>threshold |         | 0000    | DCTI threshold (0, 1, 2,, 14, 15) |      |      |           |  |

| 0      | theshold           |         |         |                                   |      |      |           |  |

|        |                    |         |         | DCTI ddx_sel                      |      |      |           |  |

| 7      | dcti_ddx_sel       |         | 1       | 0: low                            |      |      |           |  |

|        |                    |         |         | 1: hig                            | h    |      |           |  |

## TABLE 48 I<sup>2</sup>C Translator Subaddress 36 hex (DCTI\_0) [Default: 82 hex] Host Image: state st

#### TABLE 49 I<sup>2</sup>C Translator Subaddress 37 hex (DCTI\_1) [Default: 3E hex]

|     |                | Host    |         |        |      |            |  |  |

|-----|----------------|---------|---------|--------|------|------------|--|--|

| Bit | Name           | Address | Default | Func   | tion |            |  |  |

|     |                |         |         | Bit1   | Bit0 | DCTI limit |  |  |

|     |                |         |         | 0      | 0    | 0          |  |  |

| 0   | dcti_limit     |         | 10      | 0      | 1    | 1          |  |  |

| 1   |                |         |         | 1      | 0    | 2          |  |  |

|     |                |         |         | 1      | 1    | 3          |  |  |

| 2   | dcti_separate  |         | 1       | 0: off |      |            |  |  |

| 2   |                |         | 1       | 1: on  |      |            |  |  |

| 3   | dcti_          | 1D2 hex | 1       | 0: off |      |            |  |  |

| Ŭ   | protection     |         | 1       | 1: on  |      |            |  |  |

| 4   | dcti_filteron  |         | 1       | 0: off |      |            |  |  |

| -   |                |         | 1       | 1: on  |      |            |  |  |

| 5   | dcti_superhill |         | 1       | 0: off |      |            |  |  |

|     |                |         |         | 1: on  |      |            |  |  |

| 6   | reserved       |         | 0       |        |      |            |  |  |

| 7   | reserved       |         | 0       |        |      |            |  |  |

### User Manual HVS/UM9802

|        |          | Host    |         |      |      |      |               |

|--------|----------|---------|---------|------|------|------|---------------|

| Bit    | Name     | Address | Default | Func | tion |      |               |

|        |          |         |         | Bit2 | Bit1 | Bit0 | peaking alpha |

|        |          |         |         | 0    | 0    | 0    | 0             |

|        |          |         |         | 0    | 0    | 1    | 1/16          |

| 0      |          |         |         | 0    | 1    | 0    | 2/16          |

| 0<br>2 | pk_alpha |         | 010     | 0    | 1    | 1    | 3/16          |

| -      |          |         |         | 1    | 0    | 0    | 4/16          |

|        |          |         |         | 1    | 0    | 1    | 5/16          |

|        |          | 1D3 hex |         | 1    | 1    | 0    | 6/16          |

|        |          |         |         | 1    | 1    | 1    | 8/16          |

|        |          |         |         | Bit2 | Bit1 | Bit0 | peaking beta  |

|        |          |         |         | 0    | 0    | 0    | 0             |

|        |          |         |         | 0    | 0    | 1    | 1/16          |

| 2      |          |         |         | 0    | 1    | 0    | 2/16          |

| 3<br>5 | pk_beta  |         | 010     | 0    | 1    | 1    | 3/16          |

| Ŭ      |          |         |         | 1    | 0    | 0    | 4/16          |

|        |          |         |         | 1    | 0    | 1    | 5/16          |

|        |          |         |         | 1    | 1    | 0    | 6/16          |

|        |          |         |         | 1    | 1    | 1    | 8/16          |

| 6      | reserved | ]       | 0       |      |      |      |               |

| 7      | reserved |         | 0       |      |      |      |               |

## TABLE 50 I<sup>2</sup>C Translator Subaddress 38 hex (PEAK\_0) [Default: 12 hex]

### User Manual HVS/UM9802

|        |            | Host    |         |          |      |       |                  |  |

|--------|------------|---------|---------|----------|------|-------|------------------|--|

| Bit    | Name       | Address | Default | Function |      |       |                  |  |

|        |            |         |         | Bit2     | Bit1 | Bit0  | peaking tau      |  |

|        |            |         |         | 0        | 0    | 0     | 0                |  |

|        |            |         |         | 0        | 0    | 1     | 1/16             |  |

|        |            |         |         | 0        | 1    | 0     | 2/16             |  |

| 0<br>2 | pk_tau     |         | 010     | 0        | 1    | 1     | 3/16             |  |

| 2      |            |         |         | 1        | 0    | 0     | 4/16             |  |

|        |            |         |         | 1        | 0    | 1     | 5/16             |  |

|        |            | 1D4 hex |         | 1        | 1    | 0     | 6/16             |  |

|        |            |         |         | 1        | 1    | 1     | 8/16             |  |

|        |            |         | 00      | Bit1     | Bit0 | peaki | ng delta         |  |

| 2      |            |         |         | 0        | 0    | 0     |                  |  |

| 3<br>4 | pk_delta   |         |         | 0        | 1    | 1/16  |                  |  |

| -      |            |         |         | 1        | 0    | 2/16  |                  |  |

|        |            |         |         | 1        | 1    | 4/16  |                  |  |

|        |            |         |         | Bit1     | Bit0 | peaki | ng negative gain |  |

| -      |            |         |         | 0        | 0    | 0     |                  |  |

| 5<br>6 | pk_neggain |         | 00      | 0        | 1    | 1/16  |                  |  |

| 0      |            |         |         | 1        | 0    | 2/16  |                  |  |

|        |            |         |         | 1        | 1    | 4/16  |                  |  |

| 7      | reserved   |         | 0       |          |      |       |                  |  |

## TABLE 51 I<sup>2</sup>C Translator Subaddress 39 hex (PEAK\_1) [Default: 02 hex]

### TABLE 52 I<sup>2</sup>C Translator Subaddress 3A hex (PEAK\_2) [Default: 02 hex]

|        |           | Host    |         |                                        |

|--------|-----------|---------|---------|----------------------------------------|

| Bit    | Name      | Address | Default | Function                               |